RussianBostwick

n00b

- Joined

- Apr 21, 2017

- Messages

- 2

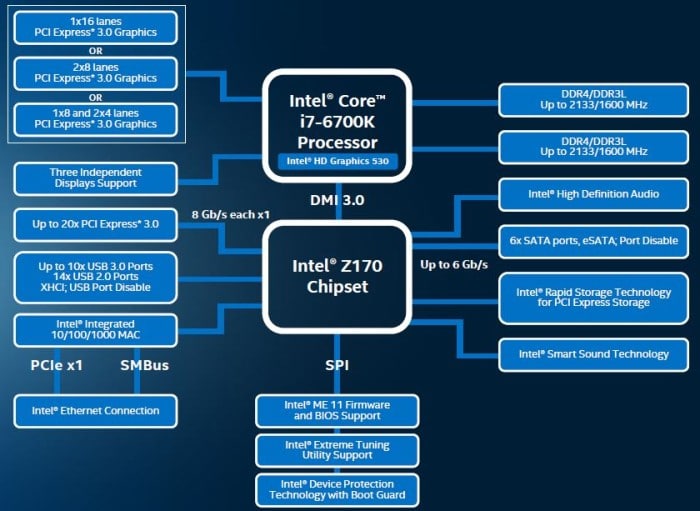

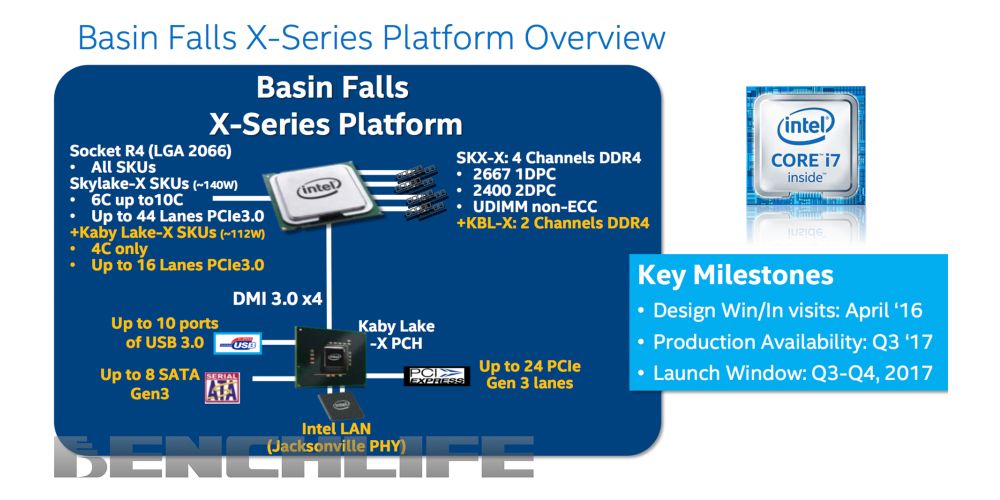

How is it that Intel is putting an extra 24 PCI-e 3.0 lanes into the 299X's PCH without massively bottlenecking like EVERY lane not to mention jamming up completely every other function of the PCH being that the PCH can only communicate with the CPU accross the DMI 3.0 x4 interface which is only capable of having a bandwidth of 8 GT/s or 3.93 GB/s when the 24 PCI-e 3.0 lanes need to themselves roughly 48 GT/s or 24 GB/s not to mention the other functions.. the last gen CPUs with 24 lanes had 16 to graphics, 4 to the DMI and 4 to etc..

Are they really selling us 24 PCI-e lanes they are shoving down a 4 lane pipe and then even counting THOSE 4 as lanes (which gave us 40 total last gen)? Isnt there an extreme bandwidth-not-being-there situation?

Are they really selling us 24 PCI-e lanes they are shoving down a 4 lane pipe and then even counting THOSE 4 as lanes (which gave us 40 total last gen)? Isnt there an extreme bandwidth-not-being-there situation?

![[H]ard|Forum](/styles/hardforum/xenforo/logo_dark.png)